|

|

|||||||||||||||||

|

|

|

|

Pull-Down-Widerstände und deren Partner, die Pull-Ups Allen RS-Flipflops gemein ist das Problem der "offenen" Eingänge. Ein solcher Eingang kann bereits durch einen über ihm schwebenden Finger vom Flipflop als gültiger Pegel erkannt werden - keine wirklich gute Sache. Die Abhilfe lautet "Pull-Down-Widerstand":

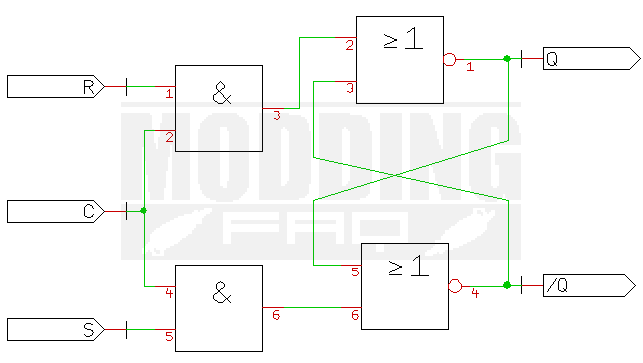

Wenn am Eingang S "gar nichts" anliegt, der Eingang also offen ist, wirkt der Widerstand als "Stütze". Über ihn liegt S nun auf Masse, ergo auf Lo-Pegel. Kommt irgendein Gatter daher und legt einen Hi-Pegel an S, fließt natürlich ein Strom in S hinein und auch über den Widerstand. Folglich muß den Widerstand nun groß genug machen, das noch genug Spannung für den Eingang des RS-Flipflops übrig bleibt (in der Regel 10K). Ein Pullup-Widerstand ist so ziemlich dasselbe: Anstatt gegen Masse ist der Widerstand gegen die Versorgungsspannung gelegt. Der anhängende Eingang liegt so immer auf Hi-Pegel, wenn ansonsten „gar nichts“ am Eingang ankommt – Pullups sind also das geeignete Werkzeug, wenn man mit NAND-aufgebauten RS-Flipflops arbeitet. Mit Pull-Widerständen ist es also möglich, Eingängen einen „Standardwert“ zu verpassen. Getaktete und ungetaktete Flipflops – was bedeutet eigentlich „Flankengetriggert“ ? Das bisher beschriebene RS-FF ist ein sogenanntes "ungetaktetes" Flipflop. Es reagiert praktisch augenblicklich auf die Änderung an den Eingängen - doch ist dies sehr oft nicht gewünscht. Eigentlich möchte man ganz genau bestimmen, wann ein FF auf seine Eingänge reagieren soll. Das ist ziemlich einfach zu machen: wir schalten einfach zwei UND-Gatter davor.

Der dritte Eingang C (Clock) ist nun ein Takt-Eingang. Erst wenn dieser Eingang einen Hi-Pegel hat, haben die Pegel an R und S überhaupt eine Wirkung. Aus dem ungetakteten RS-FF ist nun ein getaktetes FF geworden – genauer gesagt ein Taktzustandsgesteuertes (auch Level-Triggered genannt) Flipflop, denn der Pegel des Clock-Eingangs beeinflusst die anderen Eingänge. Nebenbei entfallen auch die Pulldown-Widerstände am ursprünglichen RS-Flipflop – die UND-Gatter liefern bereits definierte Pegel, die Eingänge sind also nie „offen“. Leider ist diese Lösung auch nicht perfekt. Der Taktzustand hat ein kleines Problem: Die Versorgungsspannung (auch VCC genannt). Manche Gatter (speziell die aus der TTL-Familie) benötigen eine gewisse Mindestspannung, um einen Hi-Pegel sicher zu erkennen (bei den TTL-Chips ist dies +3.6V) – ähnlicherweise gibt es eine Maximalspannung, die noch sicher als Low-Pegel erkannt wird (bei den TTL’s ist dies +0.7V). Alles dazwischen ist ein undefinierter Pegel. Wenn sich VCC nun allmählich dieser Mindestgrenze für High-Pegel nähert, kann es durch Störeinstahlungen, Spannungsschwankungen etc. zu einem „Flimmern“ kommen. Wenn also VCC auf 3.7V gefallen ist, ist das Risiko durch äußere Einflüsse sehr groß, das dieser Pegel auch mal kurzfristig auf 3.5V fällt. Das ist aber kein Hi-Pegel mehr ! Um das Problem zu lösen, erfand man die Taktflankensteuerung (auch Flankentriggerung oder Edge-Triggered genannt). Bei dieser Steuerung ist nicht der Pegel entscheidend, sondern der Wechsel des Pegels:

Takt wechselt von Hi auf Lo: Fallende Flanke -> Trigger auf fallende Flanke Daraus folgt: Bei einem auf steigende Flanken getriggerten Flipflop wird der Zustand der Eingänge erst übernommen, wenn am Clock-Eingang der Pegel von Lo auf Hi wechselt. Da ein „Flimmern“ keinen richtigen Pegelwechsel darstellt, passiert auch bei Störstrahlungen etc. nichts. Tatsächlich könnte der Clockeingang wieder auf glatten Lo-Level zurückfallen – es ändert noch immer nichts. Weiter mit: JK-FlipFlop und D-FlipFlop |

|